การสังเคราะห์ Verilog เป็นวงจรดิจิตอล และ Import เข้า Cadence (UMC 65nm Low-Leakage technology)

Verilog เป็นภาษาหนึ่งที่ใช้บรรยายฮาร์ดแวร์ (Hardware description language, HDL)

เราสามารถใช้ภาษานี้เขียนโปรแกรมให้วงจรแสดงผลลัพธ์ตามที่ต้องการได้โดยไม่ต้องต่อ

ลอจิคเกต (Logic gate) เอง จึงช่วยลดเวลาในการพัฒนาวงจรประมวลผล แต่โดยปกติภาษา

Verilog ไม่ได้แสดงลอจิคเกตหรือการเชื่อมต่อ จึงไม่สามารถนำไปวิเคราะห์การทำงานในเชิง

สัญญาณไฟฟ้า เช่น กลิทช์ (Glitch) และไม่สามารถนำไปผลิตเป็นวงจรของจริงได้

ดังนั้นเราจะต้องแปลงโปรแกรม Verilog ให้กลายเป็นวงจรลอจิคเกต

กระบวนการนี้เรียกว่าการสังเคราะห์วงจร (Synthesis)

สามารถทำได้โดยใช้โปรแกรม Cadence Encounter RTL Compiler

เมื่อเราเขียนโปรแกรม Verilog เรียบร้อยแล้วให้เปิดโปรแกรม Cadence Encounter โดยใช้คำสั่ง

$ module load ic/6.1.6 ius mmsim/12.1 assura/4.14_OA calibre/2012.2.17 rc/14.25 primetime/I edi incisive/13.1 pve/12.1 syndesign/I

$ rc -gui

ที่ Command-line โหลดไลบรารีของเทคโนโลยีที่ต้องการสร้างวงจร (ในที่นี้คือ UMC65LL)

:/> set_attribute library [ตำแหน่งไฟล์ไลบรารี นามสกุล .lib]

จากนั้นใช้ชุดคำสั่ง

:/> read_hdl [ชื่อไฟล์ Verilog นามสกุล .v]

:/> elaborate [ชื่อ entity]

:/> synthesize -to_mapped -effort high

:/> generate_reports -outdir reports -tag mapped-incr

:/> change_names -verilog

:/> write_db -to_file design.db

:/> write_design -gzip -basename design/mapped

:/> write_hdl > design.v

:/> write_sdc > design.sdc

เสร็จแล้วจะได้ไฟล์ design.v ภายในจะระบุลอจิคเกตต่างๆ และการเชื่อมต่อเพื่อให้วงจรทำงานได้

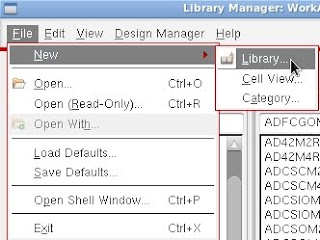

ตามที่เขียนโปรแกรมไว้ จากนั้นเปิดโปรแกรม Cadence Virtuoso เพื่อ Import ไฟล์ดังกล่าว

File -> Import -> Verilog

กำหนด

Target Library Name - ไลบรารีสำหรับเก็บวงจร

Reference Libraries - ไลบรารีของเทคโนโลยี

Verilog Files To Import - ไฟล์ design.v ที่ได้สังเคราะห์ก่อนหน้านี้

เสร็จแล้วจะได้วงจรใน Cadence สำหรับทดสอบและผลิตต่อไป

Comments

Post a Comment